# Using MMX Technology for image processing

| Student:    | Andreas Wierda                             |

|-------------|--------------------------------------------|

| Date:       | June 18, 1998                              |

| Company:    | Océ Technologies B.V.                      |

|             | P.O. box 101                               |

|             | 5900 MA Venlo                              |

| Study:      | Noordelijke Hogeschool Leeuwarden          |

|             | Engineering department                     |

|             | Technical Computer Science                 |

| Supervisors | :ir. R.J.P. Rutten (Océ Technologies B.V.) |

|             | ir. G.J. van Woudenberg                    |

|             | drs. P.J.A. van Eijk.                      |

# Preface

This report describes the results of my graduation project at the Research & Development (R&D) department of Océ Technologies B.V. in Venlo.

It is assumed that the reader is slightly familiar with computer architectures, assembly and C++ programming, but not with MMX Technology. Furthermore, it is assumed that the reader is not familiar with image processing.

During my period at Océ I have worked in pleasant way with a number of people. I specially would like to thank my supervisor, Rob Rutten. Furthermore I would like thank Marco Krom, Jan Jacobs and my fellow graduate students for the pleasant corporation. Especially Arjan v.d. Ven and Jurgen Rosendahl, who where researching familiar subjects. Finally, I would like to thank Klaas Jan Wierda for introducing me at Océ.

Venlo, June 18 1998,

Andreas Wierda

2

# Summary

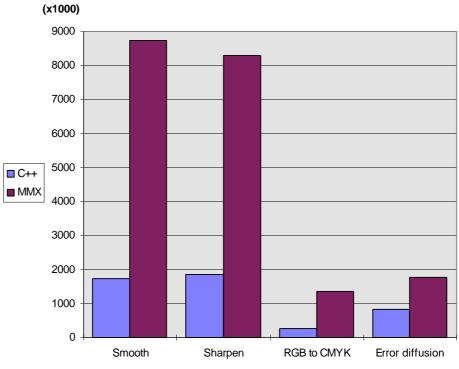

This report describes the usage of Intel's MMX Technology in image processing applications. The primary goal is to provide the reader with knowledge on the possible problems when using MMX for image processing algorithms. Additionally an indication of the possible performance improvement is given for a number of algorithm types (compared to a C++ implementation).

Before discussing implementations of specific algorithms the basic concepts of digital copying are explained. After that the Pentium processor architecture is discussed. Instead of describing the hardware this discussion focuses on the consequences of hardware features for the programmer. The most important issues to take in account when writing code are the superscalar architecture and optimal usage of the memory bandwidth (caches). Finally, MMX Technology is discussed by explaining each of the MMX instruction types.

The following algorithms have been implemented:

- Smooth

- Sharpen

- Color conversion (lookup table with interpolation)

- Halftoning (error diffusion)

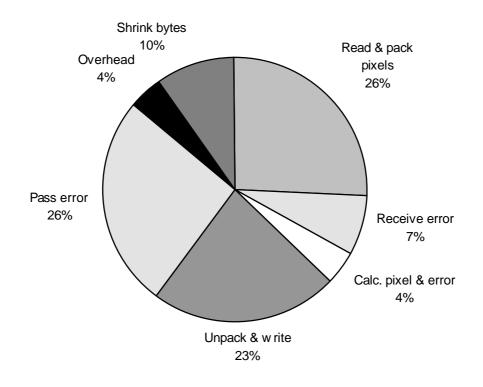

The discussion of the algorithm implementations starts with an introduction to each of the implemented algorithms. This is followed by a discussion of the main considerations made during the implementation of the algorithm in C++ and with MMX. The main considerations fall in the field of optimal image traversing and the way pixels can be processed in parallel. Next, the performance of the C++ and MMX versions are compared. Finally, an analysis of the processing time of the MMX version is made to determine the amount of processing time required for each part of the algorithm.

In the next chapter the impact of recent CPU developments on the way image processing algorithms can be implemented is discussed. Additionally the possibilities of a number of alternative CPU's are discussed (Intel Pentium II, AMD K6-2, Cyrix 6x86MX, IDT Winchip C6 and Motorola AltiVec).

In the last chapter it is concluded that the main problems encountered during the implementation of an algorithm are caused by shortcomings of the Pentium processors architecture. Additionally for some algorithms it is difficult to process pixels in parallel and very few MMX development tools are available. Using MMX results in a performance gain of a factor two to five, depending on the algorithm type.

Océ Technologies B.V. enabled the author of this report to do the research that formed the basis for this report. Océ-Technologies B.V. is not liable for the correctness of the contents and the conclusions in this report. The author is solely responsible for the contents of this report.

4

# Contents

| 1 Introduction                                       | 7  |

|------------------------------------------------------|----|

| 1.1 Background                                       | 7  |

| 1.2 Project definition                               |    |

| 1.3 Plan of action                                   |    |

|                                                      |    |

| 2 Project settings                                   |    |

| 2.1 Image processing for digital copiers             |    |

| 2.1.1 Digital copying                                |    |

| 2.1.2 Color                                          |    |

| 2.2 The processing path                              |    |

| 2.3 The test system                                  |    |

| 2.4 The Pentium Processor with MMX Technology        |    |

| 2.4.1 General features                               |    |

| 2.4.2 The superscalar architecture                   |    |

| 2.4.3 Instruction cycle times                        |    |

| 2.4.4 Caches                                         |    |

| 2.4.5 MMX Technology                                 |    |

| 2.5 Performance measurement                          |    |

|                                                      |    |

| 3 Algorithm implementation                           | 21 |

| 3.1 Introduction                                     |    |

|                                                      |    |

| 3.2 RGB Color plane separation                       |    |

| 3.2.1 The algorithm                                  |    |

| 3.2.2 The implementation                             |    |

| 3.3 Adding borders                                   |    |

| 3.3.1 The algorithm                                  |    |

| 3.3.2 The implementation<br>3.4 The smooth algorithm |    |

| 3.4.1 The algorithm                                  |    |

|                                                      |    |

| 3.4.2 C++ implementation<br>3.4.3 MMX implementation |    |

|                                                      |    |

| 3.4.4 The basic loop structure                       |    |

| 3.5 The sharpen algorithm                            |    |

| 3.5.1 The algorithm                                  |    |

| 3.5.2 C++ implementation                             |    |

| 3.5.3 MMX implementation                             |    |

| 3.6 RGB to CMYK conversion                           |    |

| 3.6.1 The algorithm                                  |    |

| 3.6.2 C++ implementation                             |    |

| 3.6.3 MMX implementation                             |    |

| 3.7 The halftoning algorithm                         |    |

| 3.7.1 The algorithm                                  |    |

| 3.7.2 C++ implementation                             |    |

| 3.7.3 MMX implementation                             |    |

| 3.8 Bits to Bytes conversion                         |    |

| 3.8.1 The algorithm                                  |    |

| 3.8.2 The implementation                             |    |

| 3.9 Removing borders                                 |    |

| 3.9.1 The algorithm                                  |    |

| 3.9.2 The implementation                             |    |

| 3.10 The total print processing path                 |    |

| 3.10.1 'Warming up' effects                          |    |

| 3.10.2 Algorithm performance                         |    |

| 3.10.3 Improvements of the processing path           |    |

| 4 Architecture developments                  | 95 |

|----------------------------------------------|----|

| 4.1 The IA32 architecture                    | 95 |

| 4.1.1 Intel Pentium Pro                      |    |

| 4.1.2 Intel Pentium II                       |    |

| 4.1.3 AMD                                    | 98 |

| 4.1.4 Cyrix                                  | 98 |

| 4.1.5 IDT                                    | 99 |

| 4.2 The PowerPC architecture                 | 99 |

|                                              |    |

| 5 Evaluation & conclusion                    |    |

| 5.1 Implementation issues                    |    |

| 5.1 Implementation issues                    |    |

|                                              |    |

| 5.1 Implementation issues<br>5.2 Performance |    |

| 5.1 Implementation issues<br>5.2 Performance |    |

7

| 1                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.1                     | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| GRT                     | Océ Technologies B.V. is one of the worlds leading producers of copiers, printers and plotters. In order to further expand Océ's market position, the Research & Development (R&D) department continuously improves existing products and develops new ones.<br>Within the R&D department, the Group Research and Technology (GRT) focuses on long term subjects. It investigates possibilities of new technologies for Océ and searches for emerging markets which might be interesting for Océ. |  |  |

| Image processing        | The last few years the well known analog copiers are gradually<br>being replaced by digital copiers, which achieve a much better<br>image quality. This image quality is, among others, achieved by<br>applying digital image processing algorithms. The hard- and<br>software required for this image processing accounts for a<br>considerable amount of the cost price. Therefore continuous<br>research is done on how to do more and better image processing<br>with less cost.              |  |  |

|                         | Since an image processing device, such as a digital copier,<br>usually contains a personal computer (PC), a considerable cost<br>reduction could be achieved when this PC is used for the<br>required image processing. However, currently the image<br>processing performance of PC's is not enough to satisfy the<br>large demands made. According to Intel MMX Technology can<br>improve the image processing performance of PC's significantly.                                               |  |  |

| 1.2                     | Project definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Problems<br>Performance | The primary goal of this project is to investigate the problems<br>encountered when implementing image processing algorithms<br>with MMX Technology. Additionally, the possible performance<br>gain when using MMX must be determined for a number of<br>algorithm classes.                                                                                                                                                                                                                       |  |  |

|                         | <ul> <li>The following algorithms will be implemented in a demo program:</li> <li>Smoothing</li> <li>Sharpening</li> <li>Color conversion</li> <li>Halftoning</li> </ul>                                                                                                                                                                                                                                                                                                                          |  |  |

| 1.3                     | Plan of action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                         | Before implementing any algorithms the Pentium architecture<br>will be studied. Additionally general knowledge of digital copying<br>and its specific properties has to be acquired.                                                                                                                                                                                                                                                                                                              |  |  |

|                         | In the main phase of the project the four algorithms will be<br>implemented. The implementation of an algorithm starts with an<br>investigation of the way the algorithm operates. Next, a<br>reference C++ implementation of the algorithm will be built. This<br>is done to understand the operation of the algorithm better<br>before implementing the algorithm with MMX. After this an MMX<br>version will be implemented. In this report the entire                                         |  |  |

development phase will be described to give the reader maximum insights in the problems encountered. Finally the performance of the C++ and the MMX version of the algorithm will be compared. To gain insights in the weaknesses and bottlenecks of MMX an analysis of the processing time will be made.

During the final phase of the project a number of alternative architectures will be investigated, focusing on the differences with MMX.

| 2                | Project settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2.1              | Image processing for digital copiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 2.1.1            | Digital copying                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Image processing | A digital copier consists essentially of an expensive scanner, a computing-core for image processing and a fast print engine.<br>Although desktop scanners and printers might seem to have ideal characteristics from the users point of view, real world scanners and printers are far from ideal and a lot of image processing has                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                  | to be performed to obtain an acceptable image quality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 2.1.2            | Color                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                  | Color can be represented using several methods. Each of these methods has its own advantages and is often specific for a certain application. The demo application uses two different color representations: RGB and CMYK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 2.1.2.1          | RGB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Human eye        | RGB (Red, Green, Blue) is a well known color representation<br>which is among others used for television and scanning<br>applications. The RGB representation is based on the way the<br>human eye perceives color. The inner back of the human eye is<br>covered with a lot of small sensors, called 'cones'. There are<br>four types of cones; one type is sensitive to all light, the other<br>three to Red, Green and Blue light respectively. To represent a<br>color in for example a scanner, the Red, Green and Blue color-<br>bases are sufficient.<br>If all three color planes of a pixel are 255 (the upper limit), the<br>pixel will be white. If all three planes are zero the pixel will be<br>black. |  |  |

| 2.1.2.2          | СМҮК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Print engine     | The RGB representation causes problems when printing,<br>because on the white paper a white pixel should be represented<br>with no ink. Therefore in print engines the complementary CMY<br>(Cyan, Magenta, Yellow) color representation is used. A white<br>pixel can then be represented with no ink, a black pixel with ink<br>of all three colors. Because of the non-ideal characteristics of the<br>ink however, the black pixel created this way has a somewhat<br>brownish color. Since this is unacceptable for text, blacK is<br>added, forming the CMYK color representation.                                                                                                                             |  |  |

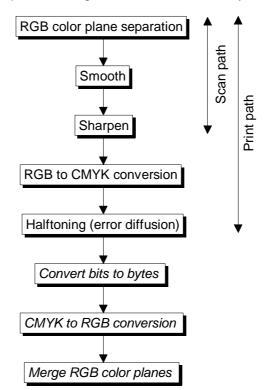

| 2.2              | The processing path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                  | There are many variations in processing-paths. The structure<br>which depends on both the desired image quality and restrictions<br>on the computational resources and architecture. Likewise, many<br>variations exist for the individual algorithms.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                  | In order to implement a wide range of algorithm classes, it was<br>chosen to implement both a scan (processing) path and a print<br>path. For algorithms such as the halftoning a number of different<br>version of varying complexity exist. It was chosen to implement                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

one of the versions, based on which the problems expected when implementing the others are predicted.

Both the sequence of the algorithms as well as the specific choices of algorithms of both paths are typical for Océ. Figure 1 shows the sequence of filter algorithms for both paths, where the right path represents the print path and the left the scan path. The italic algorithms are necessary to be able to show the processed images on a PC screen. In the processing path of a digital copier these algorithms are not necessary.

Figure 1: Processing path

Before implementing each of these algorithms a short description of them will be given, including example images.

# The test system

The development platform was a Compaq Deskpro 4000 which was also used for the performance measurements. The relevant characteristics of this PC are:

- Pentium 166 MHz Processor with MMX Technology (See section 2.4).

- An internal memory of 64 MB.

- A 256 KB level two cache.

- 2.4 GB hard disk.

- Windows NT 4.0 Workstation (Service Pack 3).

| Windows NT 4.0 | The default parameters of Windows NT were not changed,      |

|----------------|-------------------------------------------------------------|

|                | unless mentioned otherwise. The measures taken to achieve a |

|                | more constant performance are described in section 2.5.     |

Pentium 166 with MMX

2.3

# 2.4 The Pentium Processor with MMX Technology

## 2.4.1 General features

In 1997 Intel introduced the Pentium processor with MMX<sup>1</sup>. There were several changes that made the Pentium considerably faster than its predecessor, the 486:

- A dual pipeline architecture vs. a single pipeline on the 486. This so called superscalar architecture is described in section 2.4.2.

- MMX Technology<sup>2</sup> allows parallel data processing. MMX is described in section 2.4.5.

- The reduction of cycle times, especially of floating point instructions. See section 2.4.3 for more information on cycle times.

- A new branch prediction feature allows the processor to predict the destination of a branch, eliminating branch delays.

- A 64-bit databus, improving databus bandwidth (32 bit on the 486).

- 16 KB code- and 16KB datacache vs. 8K combined on the 486 (2x8 KB on the Pentium without MMX). The cache architecture and its influence on the performance is discussed in section 2.4.4.

- The branch prediction logic allows the processor to predict the destination of a branch, eliminating branch delays.

- Higher clock speeds further increased the CPU speed. On the 486 clock speeds varied from 25 MHz to 100 MHz. At its introduction the Pentium was available in a 60 and a 66 MHz version. Later versions reached clock speeds up to 233 MHz.

Some other features of the Pentium with MMX are:

- Dual processing configuration

- Fractional bus support, allowing the CPU to run at an higher clock speed than the external databus. The external databus of a Pentium CPU always runs at 66 MHz, while versions with internal clock speeds of 166, 200 and 233 MHz are available.

#### The superscalar architecture

On the predecessor of the 486, the 386 Intel introduced a pipelined architecture. Such an architecture refers to an architecture where the CPU executes each portion of an instruction in different stages. When a stage is completed, another one begins executing in the first stage, while the previous instruction moves to the second stage.

2.4.2

<sup>&</sup>lt;sup>1</sup> There are a number of differences between the conventional Pentium and the Pentium with MMX. The most important one obviously is MMX. Additionally, the Pentium with MMX has an improved branch prediction and larger caches. The conventional Pentium is not discussed further.

<sup>&</sup>lt;sup>2</sup> MMX is sometimes believed to stand for MultiMedia eXtensions or Matrix Math eXtensions. According to Intel however MMX is not an acronym.

| Pipelining       | <ul> <li>A five stage pipeline might be divided into the following stages:</li> <li>1. Fetch instruction opcode from memory</li> <li>2. Decode instruction opcode<sup>1</sup></li> <li>3. Calculate operand<sup>2</sup> address and read operand from memory</li> <li>4. Execute instruction</li> <li>5. Write instruction result</li> </ul>                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | If each stage takes 1 cycle this architecture might reach execution times of 1 cycle per instruction, compared to 5 cycles per instruction for the non-pipelined equivalent.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pipeline delays  | There are two situations where there is a significant delay in the pipeline.<br>First, if a jump is encountered, the entire pipeline has to be flushed and reloaded.<br>Second, if one of the instructions takes more than one cycle to read the operands, while the other stage still require one cycle, the preceding stages of the pipeline will stall, since they have to wait for the next stage to complete the previous instruction.                                                                                                                                                                                                |

| ʻu' and ʻv'-pipe | The superscalar architecture introduced with the Pentium<br>basically consists of two parallel pipelines, each divided into five<br>stages. When running at maximum speed, two instruction results<br>per clock cycle can be produced. The pipelines of the Pentium<br>are called the 'u'-pipe and the 'v'-pipe.                                                                                                                                                                                                                                                                                                                           |

|                  | Unfortunately only the 'u'-pipe can execute all instructions. The 'v'-pipe can only execute 'simple' integer instructions, floating point and MMX instructions. Simple integer instructions are for example move instructions, the various additions/subtractions and logical instructions.<br>Memory accesses can only be made from the 'u'-pipe. Another exception is made for read-write dependencies; if the first instruction changes an operand of the second instruction they cannot be executed parallel, and the second pipeline will stall until the first instruction finishes.                                                 |

| Pairing          | When two instructions can be executed simultaneously, i.e. the<br>first in the 'u'-pipe, and the second in the 'v'-pipe they are said to<br>pair. A pairing rate of for example 50% indicates that half of the<br>instructions can be paired with another instruction, thus reducing<br>execution times by 25% (assuming that all instruction take the<br>same number of cycles).<br>The complete list of paring rules is described in "Pentium<br>Processor Family Developers Manual" [5], chapter two.<br>Examples and further information on paring issues can be found<br>in "Pentium Processor Optimization Tools" [9], chapter nine. |

| Pairing a filter | After a filter has been programmed the code has to be paired.<br>When pairing code the statements are re-ordered in such a way<br>that that the CPU can execute two instructions parallel.<br>Intel provides the tuning program VTune. This program<br>simulates the behaviour of a CPU, and logs the required<br>processing time. VTune also indicates why two instructions will<br>not pair.                                                                                                                                                                                                                                             |

<sup>&</sup>lt;sup>1</sup> The hexadecimal code of the executed statement. <sup>2</sup> The data element the operation is performed on or with.

| General pairing rules | <ol> <li>Although it is not necessary to learn the complete list of pairing rules, a few basic rules are still necessary:</li> <li>If the first instruction modifies a register that is used by the second they will not pair.</li> <li>Only one MMX shift unit is available. This means only one MMX shift instruction can be performed, either in the 'u'- or in the 'v'-pipe. The pack and unpack instructions also use the shift unit.</li> <li>MMX memory moves can only be issued in the 'u'-pipe.</li> <li>Add instructions do not pair with MMX memory moves.</li> <li>When writing data to memory the data has to be ready one cycle in advance before the memory move.</li> </ol> |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       | These are a few of the paring rules for MMX instructions. To indicate the complexity of the total set of pairing rules; the complete list by Intel is 11 pages long.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                       | It is important to keep the pairing in mind when programming the<br>filter; use all registers instead of using one register multiple<br>times for a number of tasks. This allows two (independent)<br>blocks of code to be merged, running the first block in the 'u'-<br>pipe, the second in the 'v'-pipe. Care also has to be taken not to<br>use non-pairable instructions, especially for non-mmx<br>instructions.                                                                                                                                                                                                                                                                      |  |

| Perfect pairing       | A pairing rate of 100% is possible by moving read and calculate operations from the beginning of the loop to the end of the loop <sup>1</sup> . This is necessary because when pairing the code, instructions that can be delayed are shifted down, and instructions that use recourses not used by other instructions are moved up. At the end of the loop however, it is not possible to move instructions down, commonly resulting in a number of not pairable instructions. If some instructions from the top of the loop are moved to the end, it is possible to pair them with the instructions that otherwise would not be pairable.                                                 |  |

|                       | It was mentioned before to take care not to switch related<br>statements. However, especially memory dependencies are<br>easily overseen. It is therefore inevitable that mistakes will be<br>made. If these mistakes are not noticed the consequences are<br>disastrous; it is virtually impossible to find bugs in paired code<br>because the logic between statements is completely lost <sup>2</sup> .                                                                                                                                                                                                                                                                                  |  |

<sup>&</sup>lt;sup>1</sup> And of course just before the beginning of the loop. If this is skipped, the first loop cycle will not perform all the required operations. <sup>2</sup> While pairing the smooth algorithm a mistake was made. The mistake was made in a group of

<sup>&</sup>lt;sup>2</sup> While pairing the smooth algorithm a mistake was made. The mistake was made in a group of about ten statements, but undoing the moves was not possible because Visual C++ had been shut down. After spending three hours searching for the misplaced statement. it was decide to start pairing all over again with a non-paired version of the filter.

| Guidelines for safe pairing | <ol> <li>In this paragraph some guidelines are given that help limit the consequences of errors made while pairing the code:         <ol> <li>Back up previous versions.</li> <li>Number each statement before starting to pair the code.</li> <li>After pairing about ten to twenty statements, test the filter code.</li> </ol> </li> <li>Test the filter by subtracting the filters result byte-wise from the result of the unpaired code previously stored, for example with Paint Shop Pro. Errors can cause subtle changes in the image.</li> <li>Do not close Visual C++ before the new version of the code passed a thorough test. If Visual C++ is closed, it is not possible to undo actions.</li> </ol> <li>Do not use test images that contain large areas of the same color. Such images are sometimes processed correct, although the code is corrupted.</li> |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2.4.3                       | Instruction cycle times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                             | One of the major improvements of the Pentium compared to the 486 is the reduction of instruction cycle times. For example a floating point add takes 23 to 72 cycles on a 386, 8 to 32 on a 486 and 1 to 3 on a Pentium. Besides the floating point instructions, quite a number of other instructions were also improved. The return instruction for example takes 11 cycles on a 386, 5 on a 486 and just 2 on a Pentium.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Memory accesses             | The cycle times for instructions that read and write to memory<br>are based upon the assumption that the data can be read (or<br>written) from the level one cache. In most situations however,<br>that will not be the case, and severe delays will occur. For more<br>information on cache and memory issues see section 2.4.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 2.4.4                       | Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Code and data cache         | The first series of the Pentium had a separate code and data cache of each 8 KB, vs. 8 KB combined on the 486. There are some advantages in having the code and data cache separated. This separation generates fewer internal bus conflicts that could cause delays. But more important, this allows the code cache to contain additional information about each byte in the cache, for example instruction pairing information.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Cache lines                 | The later versions of the Pentium, those who where equipped<br>with MMX Technology, have a separate code- and data cache of<br>16 KB each. The cache consists of 512 lines of 32 bytes each.<br>Every time a data item is read which is not cached, the<br>processor will read an entire cache line from memory. The cache<br>lines are always aligned to a physical address divisible by 32.<br>When a data element is spread over multiple cache lines, a read<br>takes at least 3 clock cycles extra because the CPU can not read<br>data spread over multiple cache lines. (The read is split up in<br>two reads, after which the data is merged). This is called a Data<br>Cache Unit (DCU) Split.                                                                                                                                                                     |  |

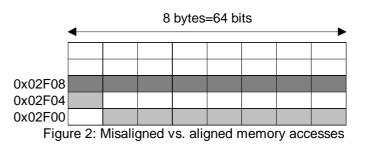

| Misaligned data             | Another delay of 3 clock cycles occurs when reading misaligned data. Intel recommends data to be aligned on the boundaries shown in the list below for optimal performance <sup>1</sup> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

<sup>&</sup>lt;sup>1</sup> Source: "Intel Architecture Optimization Manual " [8], section 3.4.2.

| • | Bytes (8 bit):        | On any boundary.                     |

|---|-----------------------|--------------------------------------|

| • | Words (16 bit):       | Align data to be contained within an |

|   |                       | aligned 4-byte doubleword.           |

| • | Doublewords (32 bit): | On any boundary which is a multiple  |

|   |                       | of four.                             |

|   |                       |                                      |

Quadwords (64 bit): On any boundary which is a multiple of eight.

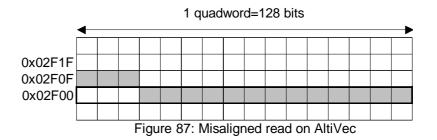

For example, a quadword read from address 0x02F01 is not aligned (light gray in Figure 2), and takes three clock cycles more to read than a quadword on address 0x02F08 (dark gray).

The cache is set-associative. This means that a cache line can not be assigned to arbitrary memory addresses. To determine the cache line and the position within a cache line, a physical address is split up like shown in Figure 3.

| bit 31                                               | 12 | 11 5            | 4 0             |  |

|------------------------------------------------------|----|-----------------|-----------------|--|

|                                                      |    | cache set value | byte nr in line |  |

| Figure 2: Manning a physical address to a sache line |    |                 |                 |  |

Figure 3: Mapping a physical address to a cache line

The seven bits for the cache set value are used to address 128 set values. The four least significant bits indicate the byte number of the physical address within the cache line.

For each of the 128 set values, four cache lines are available. Thus, a cache line address is composed as shown in Figure 4.

| bit  | 8 2              | 1  | 0   |     |

|------|------------------|----|-----|-----|

|      | cache set value  |    |     |     |

| Figu | re 4: Cache line | ac | ldı | ess |

The seven cache set value bits are the same bits as in the physical address, allowing 128 set values. The two least significant bits allow four cache lines per set value.

The consequence of this is that the cache can hold no more than four different data blocks with the same set value (bits 5 to 11) of the address.

Level two cache Level two cache Evel two Evel two cache Evel two Evel two cache Evel two Evel two Evel two Evel two Evel two Evel two Evel Evel two Evel two Evel Evel two Evel two

Set associative

| Memory             | If the data is not available in the level two cache, it has to be<br>read from memory. This takes between 200 and 300 ns. For our<br>166 MHz CPU this would be 33 to 50 clock cycles.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                    | When a write is performed to an address which is not in the level<br>one cache, then the value will go right through to the level cache<br>or to the RAM, depending upon the implementation of the<br>motherboard. This takes approximately 100 ns, causing a delay<br>of 17 cycles (on our 166 MHz system).<br>The Pentium with MMX has four write buffers. This means that<br>up to four unfinished writes to uncached memory can be done<br>without delaying the subsequent instructions.                                                                                             |  |  |  |  |  |  |

| Address generation | The last cache related issue we will discuss here is the so called<br>Address Generation Interlock (AGI). This delay is caused by the<br>fact that it takes one clock cycle to calculate the address needed<br>by an instruction which accesses memory. Normally, this<br>calculation is done in a separate stage of the pipeline, while the<br>preceding instruction is executing. But if the address depends on<br>the result of an instruction executing in the preceding clock<br>cycle, an extra cycle is needed in order to calculate the address.<br>This is called an AGI stall. |  |  |  |  |  |  |

| 2.4.5              | MMX Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

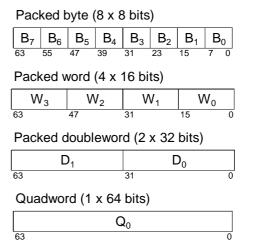

|                    | In 1996 Intel introduced MMX Technology. Basically MMX provides a set of SIMD (Single Instruction Multiple Data) instructions, allowing processing of multiple data elements in one instruction.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Data types         | <ul> <li>MMX Technology introduces 57 new instructions, 4 new data types and 8 MMX registers. The basic data type is the packed fixed point integer, which can be used in the following configurations:</li> <li>Packed byte. Eight bytes combined in a 64 bit quantity.</li> <li>Packed word. Four words packed in a 64 bit quantity.</li> <li>Packed doubleword.</li> <li>Quadword. One 64 bit quantity.</li> </ul>                                                                                                                                                                    |  |  |  |  |  |  |

|                    | The first three data types are called packed data. The MMX instructions operate on groups of eight bytes, four words two doublewords or one quadword, as shown in Figure 5.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

Figure 5: MMX data types

MMX Registers The MMX registers MM0 to MM7 are aliased on the general purpose floating point registers R0 to R7 and are used in the same way.

MMX Technology introduces a new arithmetic mode known as saturation arithmetic Saturation can best be explained by contrasting it with wraparound mode. In wraparound mode results that over- or underflow are truncated and only the least significant bits are returned. In saturation mode the results are clipped to the data range limits shown in Table 1.

|               | Lowe   | r limit   | Upper limit |           |  |  |

|---------------|--------|-----------|-------------|-----------|--|--|

|               | (hex)  | (decimal) | (hex)       | (decimal) |  |  |

| Signed byte   | 0x80   | -128      | 0x7F        | 127       |  |  |

| Signed word   | 0x800  | -32,768   | 0x7FFF      | 32,767    |  |  |

| Unsigned byte | 0x00   | 0         | 0xFF        | 255       |  |  |

| Unsigned word | 0x0000 | 0         | 0xFFFF      | 65,536    |  |  |

Table 1: Data type ranges

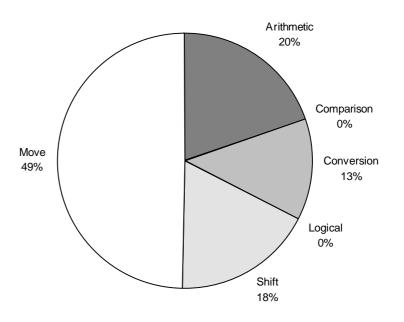

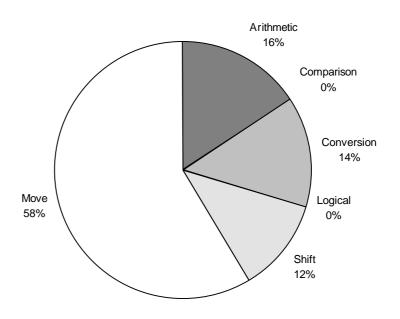

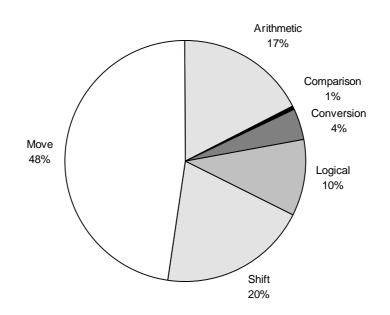

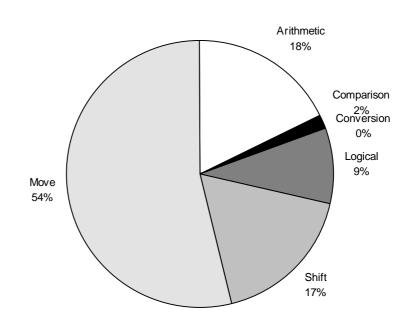

To perform actions on packed data types, Intel provides the following types of instructions:

- Arithmetic instructions

- Comparison instructions

- Conversion instructions

- Logical instructions

- Shift instructions

- Data transfer instructions

- The "Empty-MMX-State" instruction (EMMS)

Since limitations of the MMX instruction set have serious consequences on the way algorithms must be implemented, we will discuss some details of the MMX instruction set here. For a complete list of all MMX instructions, see appendix A.

Arithmetic instructions MMX provides most common arithmetic instructions, such as addition, subtraction and multiplication. The latter can only be performed on packed words, the other on packed words and packed bytes. The packed add, subtract and the packed multiply and add can also be performed on packed doublewords. However, none of the arithmetic instructions operates on a

quadword. A packed divide instruction is not available. Division can be made either with the shift-right instruction (divide by a power of 2) or by multiplying with the reciprocal.

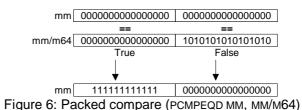

Comparison instructions Since a packed data type consists of multiple data elements, a compare instruction could not be implemented with a single zero flag as is common for normal compare instructions. Instead, the compare instruction generates a bit mask as shown<sup>1</sup> in Figure 6.

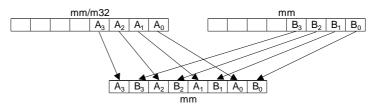

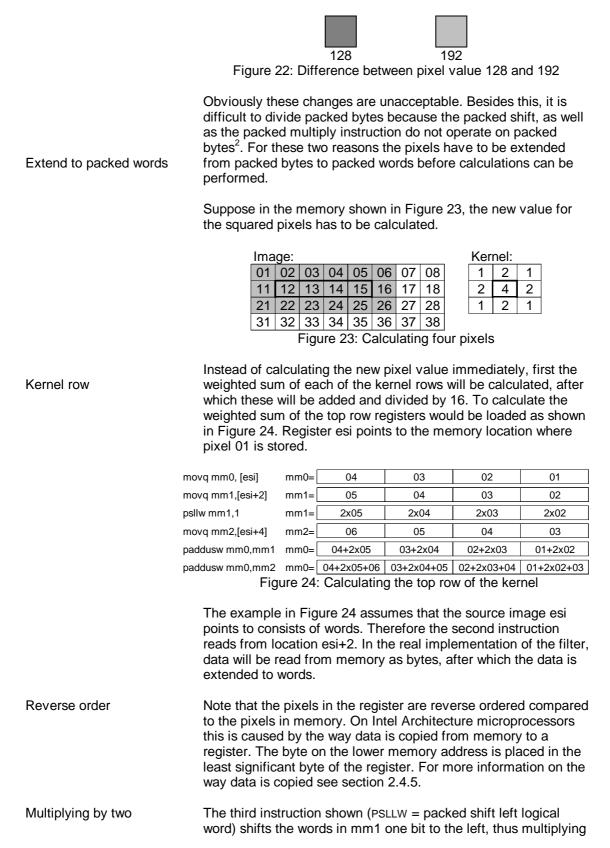

Conversion instructions The conversion instructions are used to convert packed data from one type to another. To perform an extend operation, for example to convert packed bytes to words, the packed unpack instruction must be used. If in the example in Figure 7 the mm/m32 operand is filled with zeroes, the mm operand is extended from the packed byte data type to packed words.

Figure 7: Unpack operation (punpcklbw mm, mm/m32)

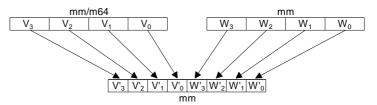

The complement of the unpack is the pack instruction (see Figure 8). This instruction can be used to shrink packed data types, for example from packed words to bytes.

Figure 8: Pack operation (PACKUSWB MM,MM/M64)

PACKUSWB stands for "Pack Unsigned with Saturation Words to Bytes". Thus, when the value of a unsigned packed word exceeds the range of the unsigned packed byte, the result is saturated.

The packed logical instructions are similar to those that operate on non-packed data types, except that the result is placed in a bit mask in the first (=destination) operand, similar to the packed compare instructions.

Logical instructions

$<sup>^{1}</sup>$  mm = MMX register.

m32 = Memory location (32 bits).

m64 = Memory location (64 bits).

Shift instructions The MMX instruction set has three shift instructions; logical shift left and right and arithmetic shift right. The arithmetic shift right instruction is needed to divide -by a power of 2-. The difference between the arithmetic shift and the logical shift is that the latter also shifts the sign bit, unlike the arithmetic shift which skips this bit. The arithmetic shift left can be done with a logical shift left combined with some code to preserve the sign bit.

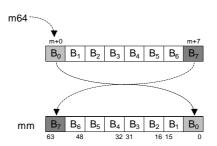

Data transfer instructions Data transfers can performed with the move instructions. When using these instructions to move packed data between registers an exact copy of the destination register is made. Care has to be taken when moving packed data from memory to an MMX register; the byte on the memory location with the highest address is placed in the most significant byte of the packed data type, as show in Figure 9.

Figure 9: MMX memory move operation (MOVQ MM,M64)

- Immediate operandsMost instructions do not accept immediate operands, for<br/>example to add '1' to all of the eight packed bytes. They only<br/>accept MMX registers or memory operands. An exception is<br/>made for the shift instructions, which accept an immediate<br/>operand for the number of bits to shift.'EMMS' instructionA special MMX instruction is the EMMS instruction. This<br/>instruction clears the internal state registers of the MMX unit.<br/>The EMMS instruction is necessary because the MMX registers

- The EMMS instruction is necessary because the MMX registers are mapped to the floating point registers. The next floating point instruction after the EMMS instruction takes 57 cycles extra to execute, thus mixing floating point and MMX instructions must be avoided at all costs.

- Cycles times As far as the cycle times of regular MMX instructions are concerned; they all take one cycle, except for instructions that use the MMX multiply unit<sup>1</sup>. The results of these instructions are available three cycles after the instruction has been started. An average throughput of one instruction per cycle can be reached by starting a number of result-independent multiplies consecutively.

# 2.5 Performance measurement The time necessary to apply each filter is measured by reading the time stamp counter register of the Pentium CPU before and after the call to the filter function. The time stamp counter

the time stamp counter register of the Pentium CPU before and after the call to the filter function. The time stamp counter register is a 64 bits wide register that is incremented one each clock cycle.

<sup>&</sup>lt;sup>1</sup> The multiply unit is used by the packed multiply and the packed multiply-and-add instructions.

| Cycles/pixel             | The time needed to process one pixel is calculated by dividing the number of clock cycles that passed by the number of pixels processed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multitasking             | <ul> <li>Windows NT is a multitasking operating system. This implies that an applications performance also depends the other processes running. Even if all other applications are shut down, in the background Windows NT still runs internal processes, called services, such as the spooler service and the TCP/IP service. To reach constant performance of the filter, all services possible where shut down. Two services can not be shut down:</li> <li>1. The eventlog service .</li> <li>2. The RPC service.</li> </ul>                                                                                                                                                                                                                                                                                  |

|                          | It is expected that the influence of these services on the filter<br>applications performance will be minimal, because they are just<br>two of the nine services running normally. Besides shutting down<br>most services, the test application has been given maximum<br>scheduling priority <sup>1</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Disk swap                | Windows NT uses, like all modern operating systems, virtual<br>addressing. Virtual addressing allows the usage of more memory<br>than physical available in the computer. This is done by mapping<br>the virtual address either to a physical memory address (the data<br>is loaded into the physical memory), or to a location on the hard<br>disk. In the latter situation the data is said to be 'swapped' to the<br>disk. Windows NT manages address mapping in such a way that<br>a data block requested by an application is loaded in the<br>physical memory. This so called 'disk swap' dramatically<br>influences the filter applications performance. By closing all<br>other application, most of the disk swapping can be prevented.<br>However, if the filter application allocates more memory than |

|                          | physically available in the PC, Windows NT will have to swap data to the hard disk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Allocating memory        | <ul> <li>Therefore the filter application has to allocate the required memory in such a way that no swapping will occur in critical sections:</li> <li>1. Minimise the amount of allocated memory.</li> <li>2. Allocate memory outside the (timed) filter functions.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                          | Further research is required on how to achieve constant processing performance on a Windows NT platform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fastest reproducible run | When measuring filter performance a number of measurements where performed, out of which the fastest that could be reproduced was documented. It was chosen to record the fastest reproducible measurement instead of the average because the slower measurements are heavily influenced by the time Windows NT needs to swap data to the hard disk <sup>2</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                |

<sup>&</sup>lt;sup>1</sup> This is done with the Windows NT Task Manager. 2 A disk access requires several milliseconds, while a CPU clock cycle is about 6 nanoseconds (based on a clock speed of 166 MHz).

| 3                  | Algorithm implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Image Gear         | The application framework needed to test the algorithms is built<br>using the MFC-Application wizard provided with Microsoft Visual<br>C++ 5.0. The wizard generates a customised application<br>template, containing for example menu's and toolbars. Reading<br>and writing of images has been implemented using the Image<br>Gear function library. The image is read by Image Gear from the<br>harddisk into memory as a linear sequence of pixels. Each pixel<br>is represented by 24 bits. For each of the Red, Green and Blue<br>color planes 8 bits are used, giving a Red, Green and Blue range<br>from 0 to 255. Within each pixel the planes are placed in Blue -<br>Green - Red order. |

| C++ vs. MMX        | <ul> <li>In the test application two versions of the processing paths are implemented; one written in standard C++, another using in-line assembler with MMX Technology. It has been decided to implement the filters in C++ for two reasons:</li> <li>1. To find out each filters typical difficulties.</li> <li>2. To be able to compare the performance of the MMX implementation to a conventional C++ implementation.</li> </ul>                                                                                                                                                                                                                                                              |

| Time stamp counter | A test session is started by choosing either the "C processing<br>path" or the "MMX processing path" option from the image<br>menu. Then the required main processing function ('FilterC' or<br>'FilterMmx') is called. These two functions are the base of the<br>processing path. They allocate all the required storage space<br>and call the specific filter functions. The required processing<br>time<br>is measured by reading the time stamp counter register before<br>and after the call to the filter function (see section 2.5).                                                                                                                                                       |

|                    | When the users starts a test session, a dialog box is displayed in<br>which the user can select the filters to execute. When the image<br>processing is completed, another dialog box is displayed<br>containing the number of cycles per pixel and the number of<br>milliseconds for each of the applied filters.                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2                | RGB Color plane separation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.2.1              | The algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    | The filters in the processing path (smooth, sharpen) will be<br>applied to each of the individual color planes. In the image<br>however, the pixels are stored in a 3x8 bits block, where the first<br>eight bits represent the Blue value, the middle eight Green and<br>the last eight Red.<br>For an easier and faster <sup>1</sup> implementation of the filters, a function<br>is built that separates the three color planes, as well as its<br>complement, a function that merges the three planes.                                                                                                                                                                                         |

| 3.2.2              | The implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | The implementation of the separate function is easy. A loop runs through the array containing the image and puts of every group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

<sup>&</sup>lt;sup>1</sup> Faster because memory reads are less cluttered up.

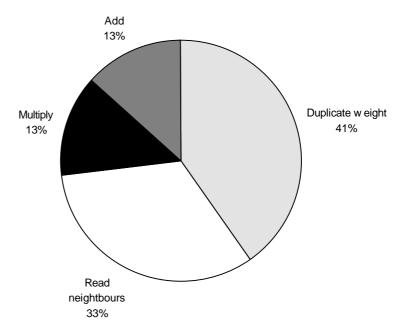

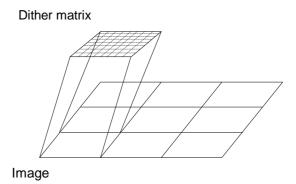

|                        | of three bytes the first byte in the Blue color plane array, the second into the Green, and the third into Red color plane array.                                                                                                                                                                                                                                                                     |  |  |  |  |  |